intel Agilex Logic Array Blocks နှင့် Adaptive Logic Modules

Intel® Agilex™ LAB နှင့် ALM ကျော်view

logic array block (LAB) သည် adaptive logic modules (ALMs) ဟုခေါ်သော အခြေခံအဆောက်အဦလုပ်ကွက်များဖြင့် ဖွဲ့စည်းထားသည်။ လော့ဂျစ်လုပ်ဆောင်ချက်များ၊ ဂဏန်းသင်္ချာလုပ်ဆောင်ချက်များနှင့် လုပ်ဆောင်ချက်များကို မှတ်ပုံတင်ရန်အတွက် LAB များကို သင် configure လုပ်နိုင်ပါသည်။

Intel® Agilex™ စက်များတွင် ရရှိနိုင်သော LAB တစ်ဝက်ကို Memory LABs (MLABs) အဖြစ် သင်အသုံးပြုနိုင်ပါသည်။ အချို့သောစက်ပစ္စည်းများတွင် MLAB အချိုးပိုမိုမြင့်မားနိုင်သည်။

Intel Quartus® Prime ဆော့ဖ်ဝဲလ်နှင့် အခြားသော ပံ့ပိုးပေးထားသည့် ပြင်ပပေါင်းစပ်ပေါင်းစပ်မှုဆိုင်ရာ ကိရိယာများသည် ကောင်တာများ၊ ပေါင်းထည့်သူများ၊ နုတ်စက်များနှင့် ဂဏန်းသင်္ချာလုပ်ဆောင်ချက်များကဲ့သို့သော ဘုံလုပ်ဆောင်ချက်များအတွက် သင့်လျော်သောမုဒ်ကို အလိုအလျောက်ရွေးချယ်သည်။

Intel Hyperflex™ Core Architecture၊ Intel Agilex စက်ပစ္စည်း ပြီးသွားပါပြီ။view

Hyper-Registers နှင့် Intel Hyperflex™ core ဗိသုကာဆိုင်ရာ အချက်အလက်များကို ပံ့ပိုးပေးပါသည်။ Hyper-Registers များသည် LAB သွင်းအားစုများနှင့် အထွက်များ ချိတ်ဆက်ထားသော လမ်းကြောင်းလမ်းကြောင်းများအပါအဝင် core fabric တစ်လျှောက် အပြန်အလှန်ချိတ်ဆက်ထားသောလမ်းကြောင်းတစ်ခုစီတွင် ရရှိနိုင်သောနောက်ထပ်စာရင်းအင်းများဖြစ်သည်။

Intel Hyperflex™ မှတ်ပုံတင်ပါ။

Intel Agilex စက်ပစ္စည်းမိသားစုသည် Intel Hyperflex™ core architecture ကို အခြေခံထားသည်။

Intel Agilex LAB တွင် Intel Hyperflex မှတ်ပုံတင်မှုများနှင့် သက်တမ်းကုန်ဆုံးခြင်းကို လွယ်ကူချောမွေ့စေရန် ဒီဇိုင်းထုတ်ထားသည့် အခြားအင်္ဂါရပ်များပါရှိသည်။ Intel Hyperflex မှတ်ပုံတင်မှုများကို ALMs နှင့် သယ်ဆောင်သည့် ကွင်းဆက်များတွင် ရရှိနိုင်ပါသည်။ Intel Agilex ALM ချိတ်ဆက်မှုအသေးစိတ်ပုံတွင်ပြထားသည့်အတိုင်း၊ Intel Hyperflex မှတ်ပုံတင်မှုများကို synchronous ရှင်းရှင်းလင်းလင်းပေါ်တွင်တည်ရှိပြီး လမ်းကြောင်းနှောင့်နှေးမှုကို တိုးမြှင့်ရန် သို့မဟုတ် လျှော့ချရန် သွင်းအားသွင်းများကို နာရီကိုဖွင့်ပေးသည်။ Intel Hyperflex မှတ်ပုံတင်မှုအားလုံးကို ဖွင့်ထားနိုင်ပြီး အနားယူနေစဉ်အတွင်း Intel Quartus Prime ဆော့ဖ်ဝဲက ထိန်းချုပ်ထားသည်။

Intel Agilex LAB နှင့် ALM ဗိသုကာနှင့် အင်္ဂါရပ်များ

အောက်ဖော်ပြပါ ကဏ္ဍများသည် Intel Agilex စက်ပစ္စည်းများအတွက် LAB နှင့် ALM ကို ဖော်ပြသည်။

ဓာတ်ခွဲခန်း

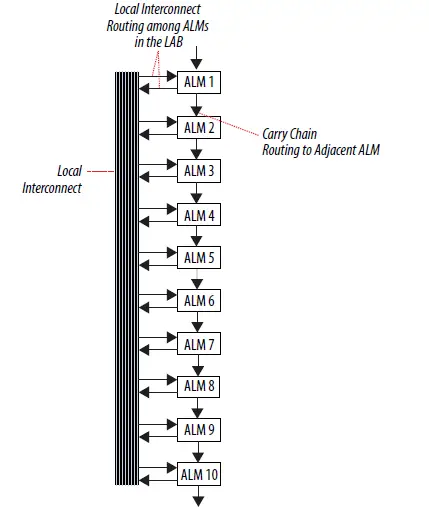

LAB များသည် လော့ဂျစ်ရင်းမြစ်များအုပ်စုတစ်ခုပါ၀င်သည့် ပြုပြင်နိုင်သော လော့ဂျစ်ဘလောက်များဖြစ်သည်။ LAB တစ်ခုစီတွင် ၎င်း၏ ALMs သို့ မောင်းနှင်ထိန်းချုပ်မှု အချက်ပြမှုများအတွက် သီးခြားယုတ္တိပါရှိပါသည်။ MLAB သည် LAB ၏ superset တစ်ခုဖြစ်ပြီး LAB အင်္ဂါရပ်များအားလုံးပါဝင်သည်။ Intel Agilex LAB နှင့် MLAB Structure ပုံတွင်ပြထားသည့်အတိုင်း LAB တစ်ခုစီတွင် စုစုပေါင်း ALM 10 ခုရှိသည်။

ပုံ ၇။

Intel Agilex LAB Structure နှင့် အပြန်အလှန်ချိတ်ဆက်မှုများ ပြီးဆုံးသည်။view

ဒီပုံက အပေါ်မှာ ပြထားတယ်။view LAB နှင့် Intel Agilex LAB နှင့် MLAB ဖွဲ့စည်းတည်ဆောက်ပုံ။

ဆက်စပ်အချက်အလက်

ဆက်စပ်အချက်အလက်

MLAB စာမျက်နှာ ၆

MLAB

MLAB တစ်ခုစီသည် ရိုးရှင်းသော dual-port SRAM ၏ အများဆုံး 640 bits ကို ပံ့ပိုးပေးသည်။ MLAB တစ်ခုစီတွင် ALM တစ်ခုစီကို 32 (depth) x 2 (width) memory block အဖြစ် configure လုပ်နိုင်ပြီး ရလဒ်အနေဖြင့် 32 (depth) x 20 (width) ရိုးရှင်းသော dual-port SRAM block ၏ configuration ကို ရရှိစေသည်။

ပုံ ၇။

Intel Agilex LAB နှင့် MLAB ဖွဲ့စည်းပုံ Local နှင့် Direct Link အပြန်အလှန်ချိတ်ဆက်မှုများ

Local နှင့် Direct Link အပြန်အလှန်ချိတ်ဆက်မှုများ

LAB တစ်ခုစီသည် ALM အထွက် 60 ကို ထုတ်ပေးနိုင်သည်။ ၎င်းတို့အနက်မှ အပိုင်းခွဲတစ်ခုသည် LAB ထည့်သွင်းမှုများကို တိုက်ရိုက်မောင်းနှင်နိုင်သော်လည်း အခြားအတန်း သို့မဟုတ် ကော်လံတစ်ခုသို့ ချိတ်ဆက်မှုတိုင်းတွင် အနည်းဆုံး ယေဘူယျရည်ရွယ်ချက်လမ်းကြောင်းပြဝါယာကြိုးတစ်ခုကို အသုံးပြုရပါမည်။

ဒေသတွင်း အပြန်အလှန်ချိတ်ဆက်မှုသည် ALM ထည့်သွင်းမှုများကို မောင်းနှင်သည်။ ALM ရလဒ်များအပြင် ကော်လံနှင့် အတန်း အပြန်အလှန်ချိတ်ဆက်မှုများသည် ဒေသတွင်း အပြန်အလှန်ချိတ်ဆက်မှုကို ဖြစ်ပေါ်စေသည်။

ပုံ ၇။ Intel Agilex LAB Local နှင့် Direct Link အပြန်အလှန်ချိတ်ဆက်မှု  ကွင်းဆက် အပြန်အလှန်ချိတ်ဆက်မှုများကို သယ်ဆောင်ပါ။

ကွင်းဆက် အပြန်အလှန်ချိတ်ဆက်မှုများကို သယ်ဆောင်ပါ။

ALM များကြားတွင် သီးခြားသယ်ဆောင်သည့်ကွင်းဆက်လမ်းကြောင်းတစ်ခုရှိသည်။ Intel Agilex စက်ပစ္စည်းများတွင် ထိရောက်သောဂဏန်းသင်္ချာလုပ်ဆောင်ချက်များအတွက် LABs များတွင် ပိုမိုကောင်းမွန်သော အပြန်အလှန်ချိတ်ဆက်ဖွဲ့စည်းပုံ ပါဝင်သည်။ ဤ ALM-to-ALM ချိတ်ဆက်မှုများသည် ဒေသတွင်း အပြန်အလှန်ချိတ်ဆက်မှုကို ရှောင်ကွင်းသည်။

LAB များ၏ ကွင်းဆက်များတစ်လျှောက် လိုက်လျောညီထွေရှိသော ပြန်လည်ချိန်ညှိခြင်းကို လုပ်ဆောင်နိုင်ရန် Intel Hyperflex မှတ်ပုံတင်မှုများကို သယ်ဆောင်သည့်ကွင်းဆက်တွင် ပေါင်းထည့်ထားပြီး Intel Quartus Prime Compiler သည် advan ကို အလိုအလျောက်ရယူသည်။tage ၏ အသုံးချမှုနှင့် စွမ်းဆောင်ရည် မြှင့်တင်ရန် ဤအရင်းအမြစ်များ။

ပုံ ၇။ ကွင်းဆက် အပြန်အလှန်ချိတ်ဆက်မှုများကို သယ်ဆောင်ပါ။ LAB ထိန်းချုပ်ရေးအချက်ပြမှုများ

LAB ထိန်းချုပ်ရေးအချက်ပြမှုများ

LAB ထိန်းချုပ်မှုပိတ်ဆို့ခြင်းတစ်ခုစီတွင် နာရီရင်းမြစ်နှစ်ခုရှိပြီး LAB နာရီနှစ်လုံး (LABCLK[1:0]) နှင့် နှောင့်နှေးနေသော LAB နာရီနှစ်ခု (LABCLK_Phi1[1:0])) ကို LAB ရှိ ALM မှတ်ပုံတင်ခြင်းနှင့် Hyper-Registers များကို မောင်းနှင်ရန်အတွက် အရင်းအမြစ်နှစ်ခုရှိသည်။ LAB သည် ALM မှတ်ပုံတင်ခြင်းများအတွက် ထူးခြားသောနာရီဖွင့်ခြင်းအချက်ပြမှုများအပြင် နောက်ထပ်ရှင်းလင်းသောအချက်ပြမှုများကို ပံ့ပိုးပေးပါသည်။

LAB အတန်းနာရီများသည် [5..0] နှင့် LAB ဒေသတွင်း အပြန်အလှန်ချိတ်ဆက်မှုများသည် LAB-wide ထိန်းချုပ်မှုအချက်ပြမှုများကို ထုတ်ပေးသည်။ နိမ့်ပါးသောနာရီကွန်ရက်သည် အတန်းနာရီများဆီသို့ ကမ္ဘာလုံးဆိုင်ရာအချက်ပြမှုများကို ဖြန့်ဝေသည်။ MultiTrack အပြန်အလှန်ချိတ်ဆက်မှုတွင် လမ်းကြောင်းထိရောက်မှုအတွက် အသုံးပြုသည့် မတူညီသောအလျားနှင့် အမြန်နှုန်းများ၏ အဆက်မပြတ်၊ စွမ်းဆောင်ရည်-အကောင်းဆုံးလမ်းကြောင်းပေါ်လမ်းကြောင်းများ ပါဝင်ပါသည်။ Intel Quartus Prime Compiler သည် ဒီဇိုင်းစွမ်းဆောင်ရည် မြှင့်တင်ရန်နှင့် စက်ပစ္စည်းအရင်းအမြစ်များကို ပိုကောင်းအောင်ပြုလုပ်ရန် ပိုမိုမြန်ဆန်သော အပြန်အလှန်ချိတ်ဆက်မှုများတွင် အရေးကြီးသော ဒီဇိုင်းလမ်းကြောင်းများကို အလိုအလျောက် လမ်းကြောင်းပေးပါသည်။

Logic Control ကိုရှင်းလင်းပါ။

LAB ကျယ်ပြန့်သောအချက်ပြမှုများသည် ALM မှတ်ပုံတင်ခြင်းအတွက် ရှင်းရှင်းလင်းလင်းအချက်ပြမှုအား ထိန်းချုပ်သည်။ ALM မှတ်ပုံတင်ခြင်းသည် synchronous နှင့် asynchronous clear နှစ်ခုလုံးကို တိုက်ရိုက်ပံ့ပိုးပေးပါသည်။ LAB တစ်ခုစီသည် synchronous clear signal တစ်ခုနှင့် asynchronous clear signals နှစ်ခုကို ပံ့ပိုးပေးပါသည်။

Intel Agilex စက်ပစ္စည်းများသည် စက်ပစ္စည်းအတွင်းရှိ မှတ်ပုံတင်ခြင်းအားလုံးကို ပြန်လည်သတ်မှတ်ပေးသည့် စက်ပစ္စည်းတစ်ခုလုံးကို ပြန်လည်သတ်မှတ်ရန်ပင် (DEV_CLRn) ကို ပေးပါသည်။ စုစည်းမှုမပြုမီ Intel Quartus Prime ဆော့ဖ်ဝဲလ်တွင် DEV_CLRn ပင်နံပါတ်ကို သင်ဖွင့်နိုင်သည်။ စက်ပစ္စည်းတစ်ခုလုံးကို ပြန်လည်သတ်မှတ်ခြင်းအချက်ပြမှုသည် အခြားထိန်းချုပ်မှုအချက်ပြမှုများအားလုံးကို လွှမ်းမိုးသည်။

ပုံ ၇။ Intel Agilex LAB-Wide ထိန်းချုပ်မှု အချက်ပြမှုများ

ALM

အောက်ပါကဏ္ဍများသည် ALM ရင်းမြစ်များ၊ ALM အထွက်နှင့် ALM လည်ပတ်မှုမုဒ်များကို အကျုံးဝင်ပါသည်။

ALM အရင်းအမြစ်များ

ALM တစ်ခုစီတွင် ပေါင်းစပ်လိုက်လျောညီထွေဖြစ်သော LUT နှစ်ခု (ALUTs)၊ two-bits full adder နှင့် register လေးခုကြားတွင် ပိုင်းခြားနိုင်သော LUT-based အရင်းအမြစ်များစွာပါရှိသည်။

ပေါင်းစပ် ALUT နှစ်ခုအတွက် ထည့်သွင်းမှု ရှစ်ခုအထိရှိပြီး ALM တစ်ခုသည် လုပ်ဆောင်ချက်နှစ်ခု၏ အမျိုးမျိုးသောပေါင်းစပ်မှုများကို အကောင်အထည်ဖော်နိုင်သည်။ ဤလိုက်လျောညီထွေရှိမှုသည် ALM အား ထည့်သွင်းမှု LUT ဗိသုကာ လေးခုနှင့် လုံးဝနောက်ပြန်-သဟဇာတဖြစ်စေနိုင်စေပါသည်။ ALM တစ်ခုသည် input function ရှစ်ခု၏ အပိုင်းခွဲတစ်ခုကိုလည်း အကောင်အထည်ဖော်နိုင်သည်။

ALM တစ်ခုတွင် programmable register လေးခုပါရှိသည်။ မှတ်ပုံတင်တစ်ခုစီတွင် အောက်ပါ port များရှိသည်။

- ဒေတာ

- Data တွေထွက်လာတယ်။

- ပုံမှန် LAB နာရီ

- နောက်ကျနေသော LAB နာရီ

- နာရီဖွင့်ပါ။

- synchronous ရှင်းပါတယ်။

- ပြတ်ပြတ်သားသား ရှင်းပါတယ်။

ကမ္ဘာလုံးဆိုင်ရာ အချက်ပြမှုများ၊ ယေဘူယျရည်ရွယ်ချက် I/O (GPIO) ပင်ချောင်းများ သို့မဟုတ် အတွင်းပိုင်းလော့ဂျစ်တစ်ခုခုက နာရီကို ဖွင့်ပေးသည့် အချက်ပြမှု၊ နာရီနှင့် ALM မှတ်ပုံတင်ခြင်း၏ ပြတ်ပြတ်သားသား သို့မဟုတ် ထပ်တူကျသည့် ရှင်းလင်းထိန်းချုပ်မှု အချက်ပြမှုများကို မောင်းနှင်နိုင်သည်။ နာရီဖွင့်ခြင်းအချက်ပြမှုတွင် ထပ်တူကျသောပြန်လည်သတ်မှတ်ခြင်းအချက်ပြမှုထက် ဦးစားပေးရှိသည်။

ပေါင်းစပ်လုပ်ဆောင်ချက်များအတွက်၊ မှတ်ပုံတင်မှုများကို ကျော်ဖြတ်ပြီး ကြည့်ရှုမှုဇယား (LUT) နှင့် adders များသည် ALM ၏ အထွက်များဆီသို့ တိုက်ရိုက်မောင်းနှင်သည်။ အမြန်အထွက်နှစ်ခုကို LUT အထွက် 6 ခုနှင့် အောက်ခြေ 5 LUT အထွက်အထွက်များအတွက် ရနိုင်သည်

ပုံ ၇။ Intel Agilex ALM High-Level Block Diagram

ALM အထွက်

ALM အထွက်

ALM တစ်ခုစီရှိ ယေဘူယျလမ်းကြောင်းပေးသည့် ရလဒ်များသည် ဒေသတွင်း၊ အတန်းနှင့် ကော်လံလမ်းကြောင်းဆိုင်ရာ အရင်းအမြစ်များကို မောင်းနှင်စေသည်။ အမြန်အထွက်လမ်းကြောင်းနှစ်ခုအပါအဝင် ALM အထွက်ခြောက်ခုသည် ကော်လံ၊ အတန်း သို့မဟုတ် တိုက်ရိုက်လင့်ခ်လမ်းကြောင်းလမ်းကြောင်းချိတ်ဆက်မှုများကို မောင်းနှင်နိုင်သည်။

LUT၊ adder သို့မဟုတ် register output သည် ALM output ကို မောင်းနှင်နိုင်သည်။ LUT သို့မဟုတ် adder နှင့် ALM မှတ်ပုံတင်နှစ်ခုလုံးသည် ALM မှတစ်ပြိုင်နက်နှင်ထုတ်နိုင်သည်။

မှတ်ပုံတင်ခြင်း ထုပ်ပိုးခြင်းသည် မသက်ဆိုင်သော မှတ်ပုံတင်ခြင်းနှင့် ပေါင်းစပ်ယုတ္တိဗေဒကို ALM တစ်ခုတည်းတွင် ထည့်သွင်းခွင့်ပြုခြင်းဖြင့် စက်ပစ္စည်းအသုံးပြုမှုကို တိုးတက်စေသည်။ ALM သည် LUT သို့မဟုတ် adder output ၏ မှတ်ပုံတင်ထားသော နှင့် မှတ်ပုံတင်ထားသော ဗားရှင်းများကို ဖယ်ရှားနိုင်သည်။

အောက်ပါပုံသည် Intel Agilex ALM ချိတ်ဆက်မှုကိုပြသသည်။ Intel Quartus Prime Resource Property Editor တွင် ALM ချိတ်ဆက်မှုတစ်ခုလုံးကို ရိုးရှင်းစေသည်။ အချို့သောလမ်းကြောင်းများကို Intel Quartus Prime ဆော့ဖ်ဝဲလ်ဖြင့် အတွင်းပိုင်းဖြတ်သွားပါမည်။

ပုံ ၇။ Intel Agilex ALM ချိတ်ဆက်မှုအသေးစိတ် ALM လည်ပတ်မှုမုဒ်များ

ALM လည်ပတ်မှုမုဒ်များ

Intel Agilex ALM သည် အောက်ပါမုဒ်များအနက်မှ လုပ်ဆောင်သည်-

- ပုံမှန်မုဒ်

- LUT မုဒ်ကို တိုးချဲ့ထားသည်။

- ဂဏန်းသင်္ချာမုဒ်

ပုံမှန်မုဒ်

ပုံမှန်မုဒ်သည် Intel Agilex ALM တစ်ခုတွင် လုပ်ဆောင်ချက်နှစ်ခုကို လုပ်ဆောင်နိုင်သည် သို့မဟုတ် တစ်ခုတည်းသော ထည့်သွင်းမှု ခြောက်ခုအထိ လုပ်ဆောင်နိုင်မည်ဖြစ်သည်။

LAB ဒေသတွင်း အပြန်အလှန်ချိတ်ဆက်မှုမှ ဒေတာထည့်သွင်းမှု ရှစ်ခုအထိသည် ပေါင်းစပ်ယုတ္တိဗေဒဆိုင်ရာ သွင်းအားစုများဖြစ်သည်။

ALM သည် လုံးဝအမှီအခိုကင်းသော လုပ်ဆောင်ချက်အချို့နှင့် ဘုံထည့်သွင်းမှုများရှိသည့် လုပ်ဆောင်ချက်အမျိုးမျိုးပေါင်းစပ်မှုများကို ပံ့ပိုးပေးနိုင်သည်။

Intel Quartus Prime Compiler သည် LUT သို့ သွင်းအားစုများကို အလိုအလျောက် ရွေးချယ်သည်။ ပုံမှန်မုဒ်ရှိ ALM များသည် ထုပ်ပိုးမှုစာရင်းသွင်းခြင်းကို ပံ့ပိုးပေးသည်။

အောက်ဖော်ပြပါပုံသည် LUT မုဒ်အတွက် မတူညီသော input ချိတ်ဆက်မှုများကို ပေါင်းစပ်ပြသထားသည်။ သင့်ဒီဇိုင်းတွင်၊ Intel Quartus Prime ဆော့ဖ်ဝဲလ်သည် စုစည်းမှုအတွင်း မတူညီသောထည့်သွင်းမှုအမည်များကို သတ်မှတ်ပေးနိုင်သည်။

ပုံ ၇။ ပုံမှန်မုဒ်တွင် ALM

ပြထားသည့် ထက်နည်းသော သွင်းအားစုများပါရှိသော လုပ်ဆောင်ချက်များကို ပေါင်းစပ်မှုများကိုလည်း ပံ့ပိုးပေးပါသည်။ ဟောင်းအတွက်ampအောက်ဖော်ပြပါ သွင်းအားစုအရေအတွက်ဖြင့် လုပ်ဆောင်ချက်များ ပေါင်းစပ်မှုများကို ပံ့ပိုးထားသည်။

- 4 နှင့် 3

- 3 နှင့် 3

- 3 နှင့် 2

- 5 နှင့် 2

ALM တစ်ခုထဲသို့ 5-input လုပ်ဆောင်ချက်နှစ်ခုကို ထုပ်ပိုးရန်အတွက်၊ လုပ်ဆောင်ချက်များတွင် အနည်းဆုံး ဘုံထည့်သွင်းမှုနှစ်ခုရှိရပါမည်။ အသုံးများသော သွင်းအားစုများမှာ dataa နှင့် datab တို့ဖြစ်သည်။ 4-input လုပ်ဆောင်ချက်ကို 5-input လုပ်ဆောင်ချက်နှင့် ပေါင်းစပ်ခြင်းသည် ဘုံထည့်သွင်းမှုတစ်ခု (dataa သို့မဟုတ် datab တစ်ခုခု) လိုအပ်သည်။

အသုံးကျဲပါးသော စက်တစ်ခုတွင်၊ ALM တစ်ခုတွင် ထားရှိနိုင်သည့် လုပ်ဆောင်ချက်များကို Intel Quartus Prime ဆော့ဖ်ဝဲလ်မှ သီးခြား ALM များတွင် အကောင်အထည်ဖော်နိုင်မည်ဖြစ်သည်။ စက်ပစ္စည်းတစ်ခု စတင်ဖြည့်သွင်းလာသည်နှင့်အမျှ Intel Quartus Prime ဆော့ဖ်ဝဲလ်သည် Intel Agilex ALM ၏ အပြည့်အဝအလားအလာကို အလိုအလျောက်အသုံးပြုသည်။ Intel Quartus Prime Compiler သည် စက်ပစ္စည်းအရင်းအမြစ်များကို အကျိုးရှိစွာအသုံးပြုရန်အတွက် ALM တစ်ခုတွင်ထားရှိရန် ဘုံထည့်သွင်းမှုများ သို့မဟုတ် လုံးဝလွတ်လပ်သောလုပ်ဆောင်ချက်များကို အသုံးပြု၍ လုပ်ဆောင်ချက်များကို အလိုအလျောက်ရှာဖွေသည်။ ထို့အပြင်၊ တည်နေရာတာဝန်များကို သတ်မှတ်ခြင်းဖြင့် သင်သည် အရင်းအမြစ်အသုံးပြုမှုကို ကိုယ်တိုင်ထိန်းချုပ်နိုင်သည်။

ပုံ ၇။ 6-ပုံမှန်မုဒ်တွင် LUT မုဒ် လုပ်ဆောင်ချက်ကို ထည့်သွင်းပါ။

ပုံ ၇။ 3-ပုံမှန်မုဒ်တွင် LUT မုဒ် လုပ်ဆောင်ချက်ကို ထည့်သွင်းပါ။

ပုံ ၇။ 3-ပုံမှန်မုဒ်တွင် LUT မုဒ် လုပ်ဆောင်ချက်ကို ထည့်သွင်းပါ။

ဒေတာနှင့် ဒေတာ b ကို စာရင်းသွင်းထုပ်ပိုးရန်အတွက် ရနိုင်ပါသည်။  အောက်ပါ input များကို အသုံးပြု၍ မည်သည့် input သုံးခုမှ ခြောက်ခုအထိမဆို အကောင်အထည်ဖော်နိုင်သည်-

အောက်ပါ input များကို အသုံးပြု၍ မည်သည့် input သုံးခုမှ ခြောက်ခုအထိမဆို အကောင်အထည်ဖော်နိုင်သည်-

- ဒေတာ

- datad0

- datac0

- datac1

- datad1

- dataf

- dataa နှင့် datab—ယင်းမှာ dataa နှင့် datab ကို LUT တစ်ခုစီတွင် မတူညီသောလုပ်ဆောင်ချက်တစ်ခုကို အကောင်အထည်ဖော်ရန် လိုက်လျောညီထွေဖြစ်စေရန်အတွက် LUT နှစ်ခုလုံးတွင် မျှဝေပါသည်။

dataa နှင့် datab နှစ်ခုစလုံးသည် register packing လုပ်ဆောင်ချက်ကို ပံ့ပိုးပေးသည်။ မှတ်ပုံတင်ထုပ်ပိုးခြင်းအင်္ဂါရပ်ကို သင်ဖွင့်ပါက၊ dataa နှင့် datab သွင်းအားစုများ သို့မဟုတ် သွင်းအားစုများထဲမှ တစ်ခုခုကို LUT ကိုကျော်ဖြတ်ပြီး အသုံးပြုထားသော မှတ်ပုံတင်မုဒ်ပေါ် မူတည်၍ မှတ်ပုံတင်ထဲသို့ တိုက်ရိုက် feed ကိုဖွင့်ပါ။ Intel Agilex စက်ပစ္စည်းများအတွက် အောက်ဖော်ပြပါ ထုပ်ပိုးထားသော မှတ်ပုံတင်မုဒ်အမျိုးအစားများကို ပံ့ပိုးပေးသည်-

- ထုပ်ပိုးထားသော မှတ်ပုံတင်လမ်းကြောင်း 5 ခုပါရှိသော 1- input LUT

- ထုပ်ပိုးထားသော မှတ်ပုံတင်လမ်းကြောင်း 5 ခုပါသော 2- input LUT

- ထုပ်ပိုးထားသော မှတ်ပုံတင်လမ်းကြောင်း 3 ခုပါသော 2-input LUT နှစ်ခု

3-Input LUT ကို Normal Mode ပုံရှိ 2-Input LUT Mode Function တွင် 3 ထုပ်ပိုးထားသော မှတ်ပုံတင်လမ်းကြောင်းများပါရှိသော 6-input LUT ကို သရုပ်ဖော်ထားသည်။ Intel Agilex စက်များအတွက်၊ XNUMX-input LUT မုဒ်သည် မှတ်ပုံတင်ထုပ်ပိုးခြင်းအင်္ဂါရပ်ကို မပံ့ပိုးပါ။

LUT မုဒ်ကို တိုးချဲ့ထားသည်။

ပုံ 11။ Extended LUT မုဒ်တွင် ပံ့ပိုးထားသော 8-Input Functions

အချို့သော 8-input လုပ်ဆောင်ချက်များကို ALM တစ်ခုတည်းတွင် LUT ထည့်သွင်းမှုများကို အသုံးပြု၍ လုပ်ဆောင်နိုင်သည်-

- ဒေတာ

- datad0

- datac0

- ဒေတာ

- ဒေတာဘေ

- datac1

- datad1

- dataf

8-input တိုးချဲ့ LUT မုဒ်တွင်၊ ထုပ်ပိုးထားသော မှတ်ပုံတင်သည့်မုဒ်ကို ပံ့ပိုးထားပြီး၊ ထုပ်ပိုးထားသော မှတ်ပုံတင်သည် dataa သို့မဟုတ် datab input ကို 8-input LUT နှင့် မျှဝေပေးခြင်းဖြင့် ထုပ်ပိုးထားသော မှတ်ပုံတင်မုဒ်ကို ပံ့ပိုးထားသည်။

ဂဏန်းသင်္ချာမုဒ်

ဂဏန်းသင်္ချာမုဒ်ရှိ ALM သည် သီးသန့်ထည့်သွင်းထားသော ပေါင်းထည့်မှုနှစ်ခုနှင့်အတူ 4-input LUT နှစ်စုံ နှစ်စုံကို အသုံးပြုသည်။ သီးခြား adders များသည် LUT များကို pre-adder logic လုပ်ဆောင်ရန် ခွင့်ပြုသည်။ ထို့ကြောင့်၊ adder တစ်ခုစီသည် 4-input လုပ်ဆောင်ချက်နှစ်ခု၏ output ကိုထည့်နိုင်သည်။

ဂဏန်းသင်္ချာမုဒ်တွင် နာရီဖွင့်ခြင်း၊ တန်ပြန်ဖွင့်ခြင်း၊ တစ်ပြိုင်တည်း အတက်အဆင်း ထိန်းချုပ်ခြင်း၊ ထည့်ခြင်းနှင့် နုတ်ခြင်း ထိန်းချုပ်ခြင်းနှင့် ထပ်တူကျအောင် ရှင်းလင်းခြင်းတို့ကိုလည်း ပေးပါသည်။

ရှင်းရှင်းလင်းလင်းနှင့် နာရီဖွင့်နိုင်သော ရွေးချယ်စရာများသည် LAB ရှိ မှတ်ပုံတင်မှုအားလုံးကို အကျိုးသက်ရောက်သည့် LAB ကျယ်ပြန့်သော အချက်ပြမှုများဖြစ်သည်။ လိုက်လျောညီထွေဖြစ်သော LUT (ALUT) တွင် မှတ်ပုံတင်အတွဲတစ်ခုစီအတွက် ဤအချက်ပြမှုများကို သင်တစ်ဦးချင်းစီပိတ်ထားနိုင်သည် သို့မဟုတ် ဖွင့်နိုင်သည်။ Intel Quartus Prime ဆော့ဖ်ဝဲလ်သည် ကောင်တာမှအသုံးမပြုသည့် မှတ်ပုံတင်များကို အခြားသော LAB များထဲသို့ အလိုအလျောက် နေရာပေးသည်။

ပုံ ၇။ ဂဏန်းသင်္ချာမုဒ်တွင် Intel Agilex ALM

ကွင်းဆက်သယ်

ကွင်းဆက်သယ်

သယ်ဆောင်သည့်ကွင်းဆက်သည် ဂဏန်းသင်္ချာမုဒ်တွင် သီးသန့်ထည့်ထားသော ဆက်စပ်ပစ္စည်းများကြားတွင် လျင်မြန်စွာသယ်ဆောင်သည့်လုပ်ဆောင်ချက်ကို ပံ့ပိုးပေးသည်။

Intel Agilex စက်ပစ္စည်းများတွင် 2-bit သယ်ဆောင်ရွေးချယ်သည့်အင်္ဂါရပ်သည် သယ်ဆောင်ကြိုးများ၏ ပြန့်ပွားမှုနှောင့်နှေးမှုကို ALM နှင့် ပိုင်းခြားပေးသည်။ သယ်ဆောင်သည့်ကြိုးများသည် LAB ရှိ ပထမ ALM သို့မဟုတ် ဆဋ္ဌမမြောက် ALM တွင် စတင်နိုင်သည်။ နောက်ဆုံး သယ်ဆောင်သွားသည့်အချက်ပြမှုကို ဒေသတွင်း၊ အတန်း သို့မဟုတ် ကော်လံ အပြန်အလှန်ချိတ်ဆက်ရန်အတွက် ပေးပို့သည့် ALM တစ်ခုသို့ ပေးပို့သည်။

Intel Agilex Logic Array Blocks နှင့် Adaptive Logic Modules အသုံးပြုသူလမ်းညွှန်များအတွက် စာရွက်စာတမ်းပြန်လည်ပြင်ဆင်ခြင်းမှတ်တမ်း

| စာရွက်စာတမ်းဗားရှင်း | အပြောင်းအလဲများ |

| 2022.05.24 | အပ်ဒိတ်လုပ်ထားသောပုံ- Intel Agilex ALM High-Level Block Diagram |

| 2019.11.14 | LAB Control Signals ကဏ္ဍတွင် ဖော်ပြချက်ကို အပ်ဒိတ်လုပ်ထားသည်။ |

| 2019.10.01 |

|

| 2019.04.02 | ကနဦး ထုတ်ဝေမှု။ |

Intel ကော်ပိုရေးရှင်း။

မူပိုင်ခွင့်ကိုလက်ဝယ်ထားသည်။ Intel၊ Intel လိုဂိုနှင့် အခြားသော Intel အမှတ်အသားများသည် Intel ကော်ပိုရေးရှင်း သို့မဟုတ် ၎င်း၏လုပ်ငန်းခွဲများ၏ အမှတ်တံဆိပ်များဖြစ်သည်။ Intel သည် Intel ၏ စံအာမခံချက်နှင့်အညီ ၎င်း၏ FPGA နှင့် တစ်ပိုင်းလျှပ်ကူးပစ္စည်းထုတ်ကုန်များ၏ စွမ်းဆောင်ရည်ကို လက်ရှိ သတ်မှတ်ချက်များအတိုင်း အာမခံထားသော်လည်း မည်သည့်ထုတ်ကုန်နှင့် ဝန်ဆောင်မှုများကိုမဆို အသိပေးခြင်းမရှိဘဲ အချိန်မရွေး အပြောင်းအလဲပြုလုပ်ပိုင်ခွင့်ကို လက်ဝယ်ရှိပါသည်။ Intel မှ စာဖြင့် အတိအလင်း သဘောတူထားသည့်အတိုင်း ဤနေရာတွင် ဖော်ပြထားသော အချက်အလက်၊ ထုတ်ကုန် သို့မဟုတ် ဝန်ဆောင်မှုကို အသုံးပြုခြင်း သို့မဟုတ် အသုံးပြုခြင်းမှ ဖြစ်ပေါ်လာသော တာဝန် သို့မဟုတ် တာဝန်ခံမှု မရှိဟု ယူဆပါသည်။ Intel သုံးစွဲသူများသည် ထုတ်ဝေထားသော အချက်အလက်များနှင့် ထုတ်ကုန် သို့မဟုတ် ဝန်ဆောင်မှုများအတွက် အမှာစာမတင်မီ နောက်ဆုံးဗားရှင်းကို ရယူရန် အကြံပြုအပ်ပါသည်။

*အခြားအမည်များနှင့် အမှတ်တံဆိပ်များကို အခြားသူများ၏ပိုင်ဆိုင်မှုအဖြစ် တောင်းဆိုနိုင်ပါသည်။

ISO

၁၁:၄၂

မှတ်ပုံတင်ထားသည်။

စာရွက်စာတမ်းများ / အရင်းအမြစ်များ

|

intel Agilex Logic Array Blocks နှင့် Adaptive Logic Modules [pdf] အသုံးပြုသူလမ်းညွှန် Agilex Logic Array Blocks and Adaptive Logic Modules, Agilex, Logic Array Blocks and Adaptive Logic Modules, Array Blocks and Adaptive Logic Modules, Adaptive Logic Modules, Logic Modules |